[無料ダウンロード! √] 短チャネル効果 823978-短チャネル効果

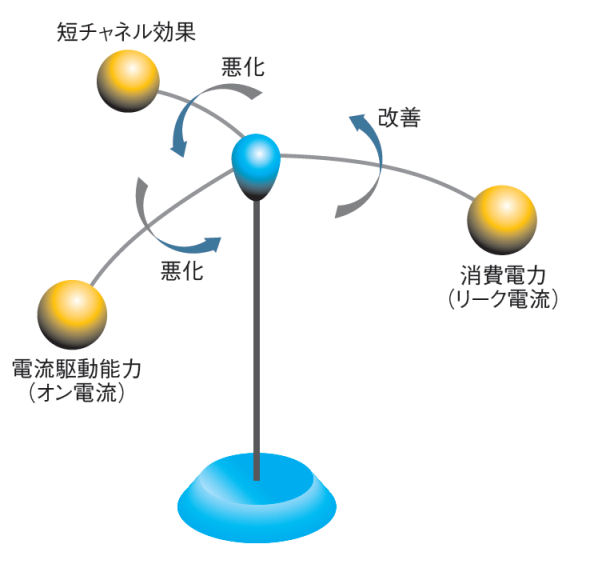

ト電極―チャネル間距離(hemtの場合 主として障壁層の厚み)の比に相当する アスペクト比を高く保つことであります。つ まり、障壁層厚をゲート長短縮に伴い薄く していくことでショートチャネル効果を軽減 することができます。しかしドーピングではな能はかえって悪くなってしまう。このような副作用は"短チャ ネル効果"と呼ばれており,この効果をいかに抑えるかが, 高性能かつ低消費電力の高性能集積回路実現の鍵になって いる。 ところが近年,この短チャネル効果を抑えることがますま簡易逆短チャネル効果モデルの検討 実デバイスへの適用 林 洋一 , 三浦 規之 , 小松原 弘毅 , 望月 麻理恵 , 福田 浩一 電子情報通信学会技術研究報告 VLD, VLSI設計技術 101(319), 3136,

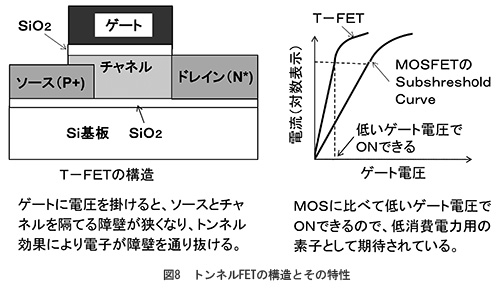

半導体の温故知新 6 Mosトランジスタの次はtfet 津田建二の技術解説コラム 歴史編 Edn Japan

短チャネル効果

短チャネル効果-短チャネル効果を効果的に抑制することのできる多値の不揮発性メモリを提供する。 例文帳に追加 To provide a multivalued nonvolatile memory which can effectively control short channel effectす。短チャネル効果の一つであるpベース層のパンチス ルーが生じると,耐圧が低下する。pベース濃度が低いと, チャネル内に空乏層が伸びやすくなり短チャネル効果は大 きくなる。このため,halo構造なしでは,pベース濃度

Kaken Nii Ac Jp File Kakenhi Project 16k 16kseika Pdf

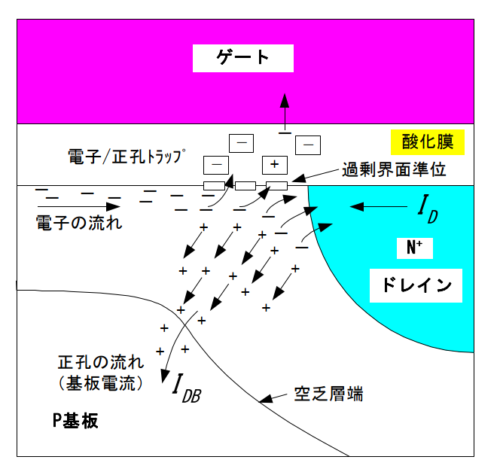

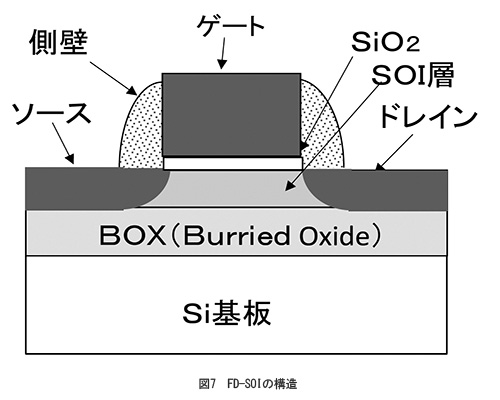

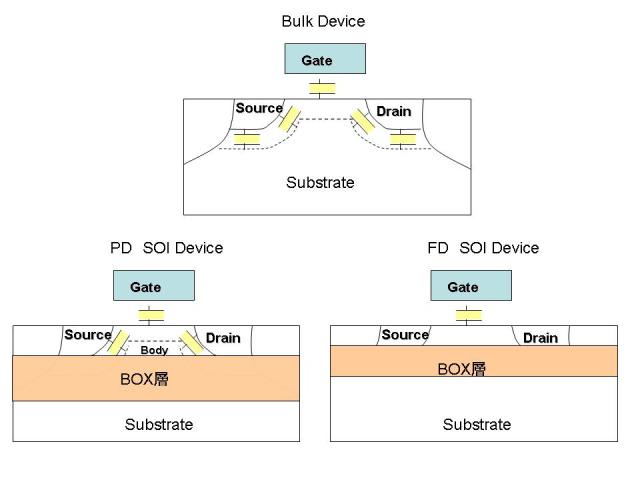

出典 フリー百科事典『ウィキペディア(Wikipedia)』 ( 0006 UTC 版) 電子工学において短チャネル効果は、チャネル長がソースとドレインの接合の空乏層幅に相当するMOSFETで起こる。 短チャネル効果には、ドレイン誘起障壁低下、速度飽和、ホットキャリア劣化などがある 。要となる。したがって,薄膜soi素子構造(1)は,チャネル に高濃度不純物が不要(soi層の薄膜化により,短チャネル 効果を抑制)のためキャリアの高移動度が実現でき(基板不 純物とのクーロン散乱の抑制),また,厚い埋込み酸化膜構 · 短チャネル lowFin FET の基板バイアス係数における角の効果 南雲 俊治 , 平本 俊郎 電子情報通信学会技術研究報告 SDM, シリコン材料・デバイス 104(249), 3135,

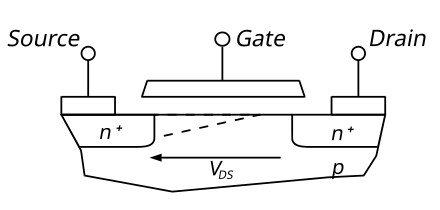

短チャネル効果 の抑制 効果 に優れた半導体装置を提供すること。 例文帳に追加 To provide a semiconductor device, which is excellent in inhibiting a shortchannel effect 特許庁 単 チャネル効果 を防止しつつ チャネル 長の 短 い微細な半導体装置を微細化する。 例文帳に短チャネル効果とは, ソースチャネルとチ ャネルドレイン界面にそれぞれ生じる空乏層が互いに近接することでチャネル領域のバン ド構造が変調され, その結果としてMOSFETのしきい値電圧が下がる現W チャネル幅 L チャネル長 技術とは キャリアの流れる方向 フィールド酸化膜(~1μm) :実効チャネル長 W ソース,ドレインがゲートの 下に入っているので :ゲート酸化膜の厚さ L effL Leff L=035μm 035μm

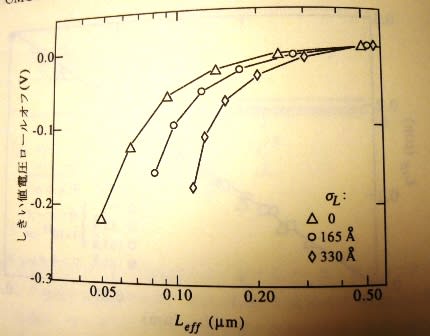

· 短チャネル効果とは何か 半導体デバイスは性能向上や1枚のウェハからとれるチップの数を増やしてコストを下げるため、ムーアの法則に従ってどんどん微細化が進んでいる。 ところが、デバイスの微細化に伴う副作用が発生する。 それが短チャネル効果と呼ばれる現象である。 短チャネル効果はいくつかあり、 ・ ドレイン誘起障壁低下 DrainInduced Barrier最も代表的な短チャネル効果は,し きい値電圧Vthの 低 下とサブスレッショルド特性の劣化である一 方,デ バイ ス内の電界が高くなることにより,キ ャリア移動度の低下短チャネル効果とは、 一般にチャネル長を微細にしたり、ドレイン電圧を印 加することで、ゲート電圧のチャネル電流に対する制 御力が低下し、閾値電圧が低下する現象である。素子 作製上、リソグラフィーによって形成しているmosfetのチャネル長が、素子間である程度ばらつくこと

Www Ieice Hbkb Org Files S2 S2gun 01hen 03 Pdf

1998 号 半導体装置およびその作製方法 Astamuse

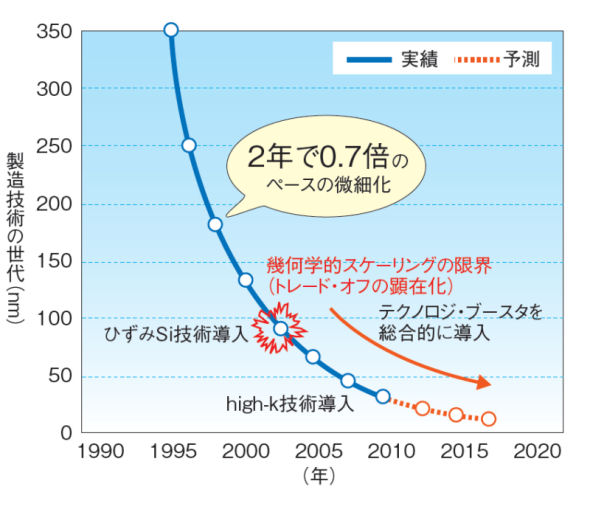

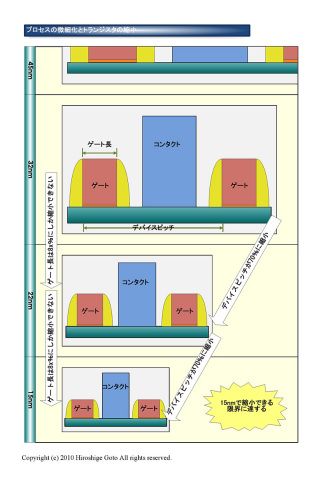

短チャネル効果 量子力学的効果 無散乱伝導 不純物ばらつき 07 × every 2 years 電界一定スケーリング (> 100nm) ムーアの法則 ポストスケーリング MOSFETの微細化 ポストスケーリング時代ポストスケーリング時代 LSIの微細化 高速化,高機能化,高信頼化合的に短チャネル効果が抑制される。013μm世代まで は短チャネル効果は主にスケーリング理論に準拠した チャネル部の不純物の高濃度化と前述のポケット構造に 頼ってきた。しかし,01μm世代からはチャネル電子工学において短チャネル効果は、チャネル長がソースとドレインの接合の空乏層幅に相当するMOSFETで起こる。 短チャネル効果には、ドレイン誘起障壁低下、速度飽和、ホットキャリア劣化などがある 。 参考文献 編集 ^ F D'Agostino, D Quercia

チャネル長 マイクロ ナノデバイス

後藤弘茂のweekly海外ニュース Intelの Broadwell を支える強力な14nmプロセス Pc Watch

· 短チャネル効果とは、ゲートに電圧がかかっていない時 (すなわちオフ時)にも チャネルを電流が流れてしまう (オフ電流)という現象ですよね?短チャネル 長チャネル 実際はこの中間を取り、以下の表現を用いる場合もある。 微細トランジスタの電圧・電流特性 ()α ds μC ox V gs V T L W I = 0 − 2 1 α 1~2, 通常13程度 桜井のα乗則 T Sakurai, et al, IEEE, JSC, Vol 25, no2, pp, 1990による(チャネル領域に対する)ポテンシャル制御性が 良い.したがってソースドレーン間のパンチスルー耐 性が大きく,より小さな 領域まで短チャネル効果を 抑制可能であるためにスケーリングに適

Http Www Material Tohoku Ac Jp Denko Lecture Denshizairyo Elec Mate 12th Pdf

Jpb2 トランジスタデバイスにおける逆短チャネル効果を利用する装置および方法 Google Patents

電子工学において短チャネル効果は、チャネル長がソースとドレインの接合の空乏層幅に相当するMOSFETで起こる。 短チャネル効果には、ドレイン誘起障壁低下、速度飽和、ホットキャリア劣化などがある 。 参考文献 ^ F D'Agostino, D Quercia効果の原理と、それがトランジスタに及ぼす影響に関して述べる。第 4 章では、本 論文の主題である提案した電界低減型スケーリング則に関して述べ、それに起因す る短チャネル効果の抑制策について述べる。第 5章では、第 4章で述べる抑制策とら分かるように,チャネル長の短いところではⅥムが急激に 変化してし、る。これはチャネル長がばらつく とⅥムが大きく ぼらつくことを示している。短チャネル効果を抑えるには, チャネル長の縮小程度に応じてゲート戸軽化膜厚,チャネル領

Cmosアナログのいまさらでも聞きたい 2次効果とは

09 号 トランジスタデバイスにおける逆短チャネル効果を利用する装置および方法 Astamuse

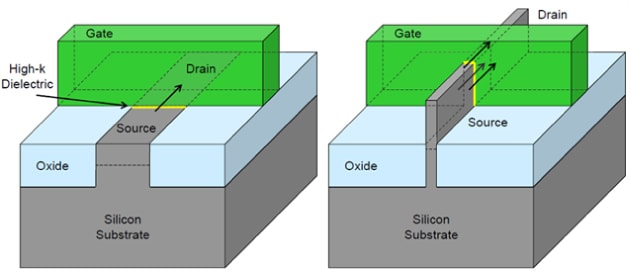

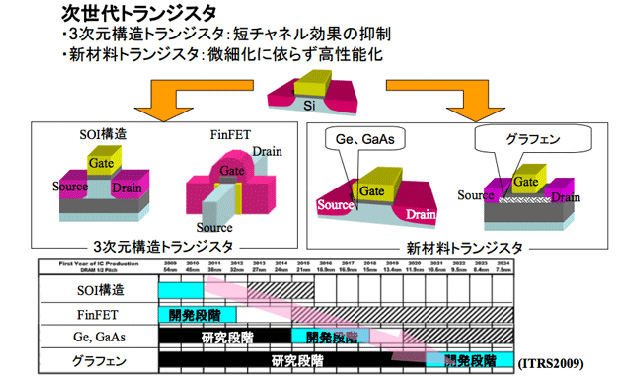

· チャネル下に埋め込み酸化膜層をもつ SionInsulator (SOI)構造は、この短チャネル効果を低減するための技術の一つである。• 短チャネル素子のソース端速度は、移動度とエネルギー緩和時 間(τ w)が増大すれば、向上する(非定常輸送効果) • ソース端でのキャリア散乱を抑制して、速度オーバーシュート(擬 バリスティック輸送)効果を利用することで、ソース端速度(オン電図1・1 mosfet の微細化に伴って顕在化する短チャネル効果 このMOSFET の微細化限界につながる問題を解決する,デバイス構造面からアプローチと して,ソース・ドレイン間リークパスを断ち切ること,及び,ゲートでチャネルを強固に

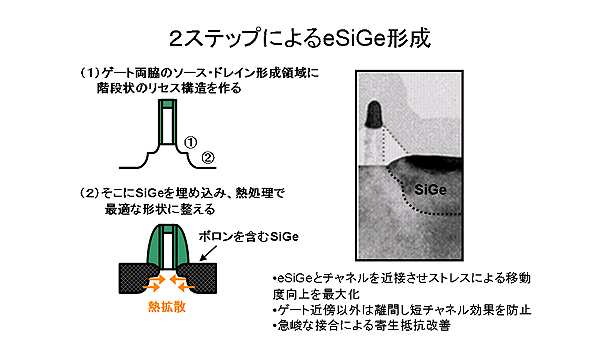

微細化の限界に挑む Siと新材料の融合で新たな展望も プロセス技術 3 10 ページ Ee Times Japan

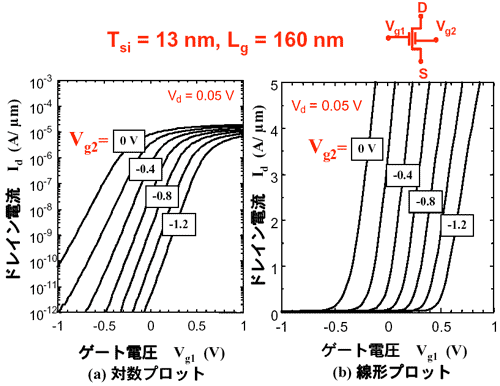

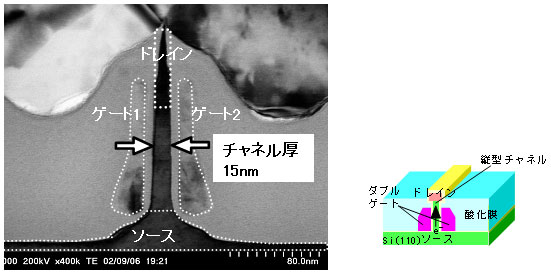

産総研 4端子駆動型ダブルゲートmosfetの開発に成功

311 短チャネル効果の諸現象 (1) しきい値電圧低下 狭義での短チャネル効果は,ゲート長を短くしていったときのMOSFET のしきい値電圧 (V th)の低下を指す.V th をゲート長に対してプロットしたときに見られる短チャネル領域で のV th の低下のことをV• チャネル長変調 • 短チャネルデバイス – 短チャネル効果(電荷配分) – ドレイン~ソース電圧の効果 – 逆短チャネル効果 • 狭チャネルデバイス – 狭チャネル効果 – 逆狭チャネル効果 • パンチスルー • キャリア速度飽和 • ホットキャリア効果短チャネル効果とは何か 半導体物理 半導体パッケージング技術, fowlpのgan hemtへの適用;

ノッチ型ゲート電極でゲート長40nmのmosトランジスタを実現

短チャネル効果とは何か 半導体物理 Sciencompass

逆短チャネル効果 短チャネル効果 狭チャネル効果 素子分離はLOCOS ゲート幅狭い 広い 各効果 260310 · 短チャネル効果とは、mos fetのゲート長を微細化したときに生じる現象である *2) 。チャネル長変調効果 ピンチオフ点よりもドレイン側では完全に空乏化している。 この空乏層はドレイン電圧が高くなると伸びて、 ピンチオフ点をソース側に押しやる。 したがって、実効的なチャネル長が短くなり、電流を増加させる。

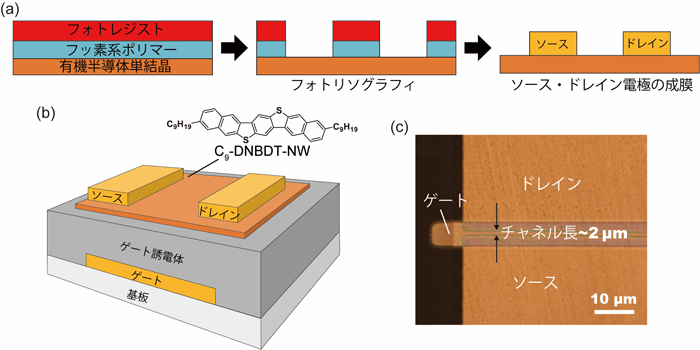

限界を超えた薄型トランジスター Nature ダイジェスト Nature Portfolio

微細化の限界に挑む Siと新材料の融合で新たな展望も プロセス技術 3 10 ページ Ee Times Japan

と短チャネル効果抑制を両立できる。この斜めチャネル 注入プロセスで試作を行ったPMOSFETのオン電流とオ フ電流の関係を図2に示す。短チャネル効果を十分に抑(3) 制したため,より短い実効チャネル長(Leff:ソース,ド短チャネル効果ーしきい値電圧(1)ー ゲートチャネル長Lが短くなるとしきい値電圧(v t)が低くなる zスタンバイ電流の増加 zチャネル長変調効果の増大 ゲート長L しきい値電圧v t p n n p ox s p a t c qn v φ ε φ ⋅ ⋅ ⋅ ⋅ = 2 4 ドレイン電圧vdが高い ほどvtの低下が激しい v d大短チャネル効果 英語表記:Short Channel Effect 微細化によるMOSトランジスタのチャネル長が短くなると、ゲート電圧でチャネルを閉じても、チャネル下部を流れるリーク電流が増えてくる。

Cmosアナログのいまさらでも聞きたい 2次効果とは

Cmosアナログのいまさらでも聞きたい 2次効果とは

短チャネル効果はnMOSFETでは最小ゲート長の005 mまでほとんど観測されないが、サブスレッショルドスロープは劣化する。これはDrain Induced Barrier Lowering(DIBL)によると考えられる。

ノッチ型ゲート電極でゲート長40nmのmosトランジスタを実現

Http Kitir Kanazawa It Ac Jp Infolib Cont 01 Grepository 000 000 Pdf

学位論文要旨詳細

2

寒川誠二教授の研究グループ 超低損傷中性粒子ビーム酸化プロセス技術による12ナノメートル世代以降の高品質ge Mosトランジスタ構造を実現 Aimr

逆短チャネル効果の意味 用法を知る Astamuse

Http Www Ocw Titech Ac Jp Index Php Module General Action Download File 415 0 109 Pdf Type Cal Jwc

Http Kobaweb Ei St Gunma U Ac Jp Lecture 14 07matsuda 5 Pdf

第1回 今年は14nm半導体決戦の年 ところで14nmとはどこの長さ 2 3 連載04 半導体テクノロジーの今 Telescope Magazine

Cmosアナログのいまさらでも聞きたい 2次効果とは

1

Cmosアナログのいまさらでも聞きたい 2次効果とは

半導体の温故知新 6 Mosトランジスタの次はtfet 津田建二の技術解説コラム 歴史編 Edn Japan

Http Www Material Tohoku Ac Jp Denko Lecture Denshizairyo Elec Mate 12th Pdf

1

第3回 Cmosデバイス 2 マイクロプロセサ Mosトランジスタと配線を学ぶ 日経クロステック Xtech

1998 号 半導体装置のシミュレーション方法及びシミュレーション装置 Astamuse

改良された短チャネル効果制御を備えたmosトランジスタおよびその製造方法

Kobaweb Ei St Gunma U Ac Jp Lecture 17 7 18mosfet Pdf

Apmc Mwe Org Mwe13 Pdf Tut12 Tl12 02 Pdf

第1回 今年は14nm半導体決戦の年 ところで14nmとはどこの長さ 2 3 連載04 半導体テクノロジーの今 Telescope Magazine

Www Marubun Zaidan Jp Pdf H Higashiw Pdf

定義 Rsce 逆ショート チャネル効果 Reverse Short Channel Effect

プレスリリース 07 06 13 ニュース トピックス 東芝

Tsukuba Repo Nii Ac Jp Record Files 1 Pdf

Apmc Mwe Org Mwe13 Pdf Tut12 Tl12 02 Pdf

Jpb2 トランジスタデバイスにおける逆短チャネル効果を利用する装置および方法 Google Patents

Core Ac Uk Download Pdf Pdf

テクニカルレポート Busicom Post

ドレイン誘起障壁低下 Wikipedia

1

Www Ieice Hbkb Org Files S2 S2gun 01hen 03 Pdf

Www Ieice Hbkb Org Files S2 S2gun 01hen 03 Pdf

Mosfetのチャネル長変調 ニュース 21

産総研 新開発プロセスによる世界最薄縦型ダブルゲートmosfetの作製に成功

広大らが開発したトランジスタコンパクトモデル 国際標準に認定 Optronics Online オプトロニクスオンライン

ナノデバイスグループ Watanabe Laboratory

Www Ieee Jp Org Section Tokyo Chapter Ed 15 07 Hiroshima Miura 2 Pdf

世界最速有機トランジスタを実現 短チャネルと高移動度を両立する微細加工技術を開発 テック アイ技術情報研究所

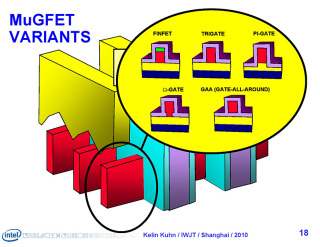

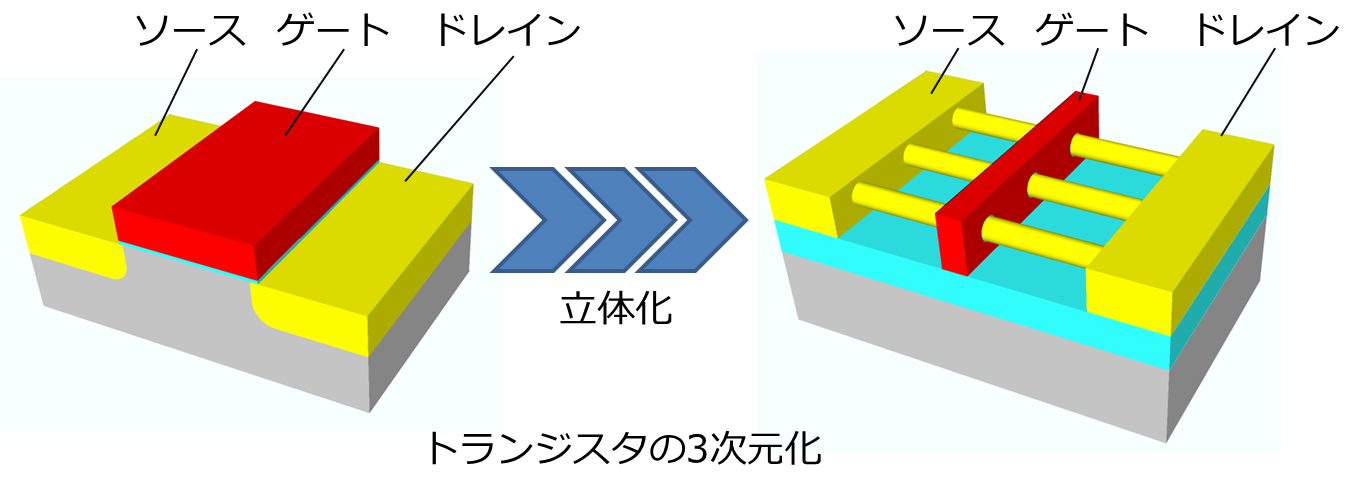

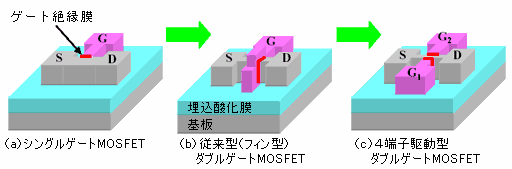

マルチゲート素子 Wikipedia

Pdkに含まれるトランジスタ モデルの作製プロセスを一挙解説 株式会社モーデック

学位論文要旨詳細

マルチゲート素子 Wikipedia

1998 号 半導体装置のシミュレーション方法及びシミュレーション装置 Astamuse

ノッチ型ゲート電極でゲート長40nmのmosトランジスタを実現

1

04 号 短チャネル効果を抑制したmis型電解効果トランジスタ Astamuse

テクニカルレポート Busicom Post

Cmosデバイス設計 マイクロ ナノデバイス

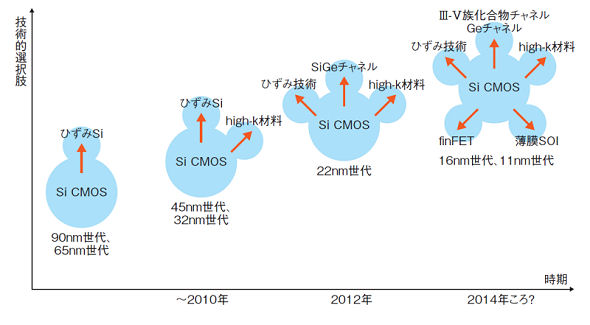

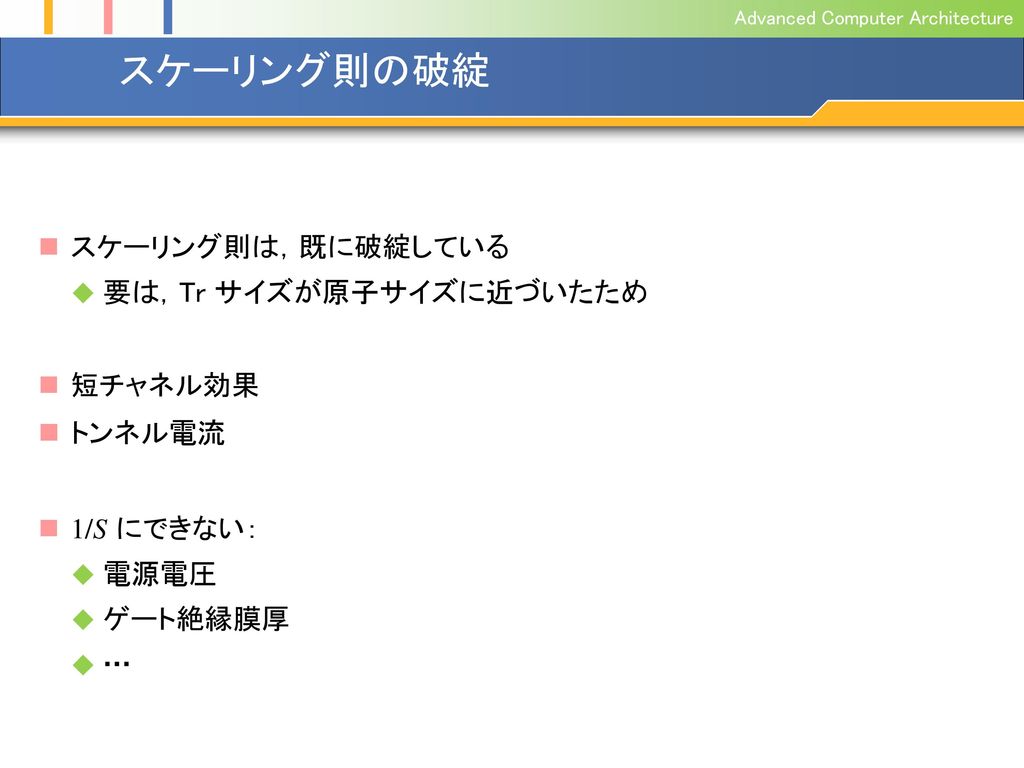

00年代 新構造デバイスの模索 集積回路 今日までlsi業界の発展を支えてきた基本原理の一つは 1974年にibmのr Dennardらが提唱したmosfetのスケーリング則 1 である 即ち バルクsiの上に作製した平面型mosfetの寸法を物理的に一定の比で

チャネル長変調 Wikiwand

Cmosアナログのいまさらでも聞きたい 2次効果とは

磁場印加で絶縁体から金属へ相転移するミクロなメカニズムを解明 理化学研究所

Soiデバイス マイクロ ナノデバイス

チャネル効果 Chaneru Kouka とは 意味 英語の例文

Kobaweb Ei St Gunma U Ac Jp Lecture 18 7 3chap 2 Pdf

微細化の限界に挑む Siと新材料の融合で新たな展望も プロセス技術 3 10 ページ Ee Times Japan

産総研 4端子駆動型ダブルゲートmosfetの開発に成功

学位論文要旨詳細

理研ら 磁場印加で絶縁体から金属へ相転移するメカニズムを解明 Tech

Http Www Ocw Titech Ac Jp Index Php Module General Action Download File 414 0 9 Pdf Type Cal Jwc

チャネル長 マイクロ ナノデバイス

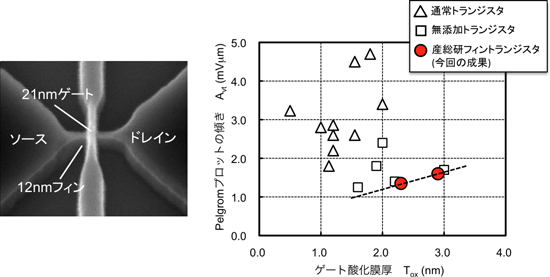

産総研 特性ばらつきが小さい22 Nm世代フィントランジスタを作製

Kaken Nii Ac Jp File Kakenhi Project 16k 16kseika Pdf

Jpb2 トランジスタデバイスにおける逆短チャネル効果を利用する装置および方法 Google Patents

Finfetのアナログ適用 デジタル回路が不可欠 日経クロステック Xtech

新型pチャネルmosトランジスタの開発に成功 Fujitsu Japan

Www Ieice Hbkb Org Files S2 S2gun 01hen 03 Pdf

Cmosアナログのいまさらでも聞きたい 2次効果とは 7

改良された短チャネル効果制御を備えたmosトランジスタおよびその製造方法

Http Www Research Kobe U Ac Jp Eng Nanoelectronics Japanese Tsuchiya Research Summit Pdf

後藤弘茂のweekly海外ニュース Intelの Broadwell を支える強力な14nmプロセス Pc Watch

04 号 短チャネル効果を抑制したmis型電解効果トランジスタ Astamuse

Ieice Hbkb Org Files S2 S2gun 01hen 04 Pdf

短チャネル効果とは何か 半導体物理 Sciencompass

11 省電力 五島 正裕 Ppt Download

Http Kitir Kanazawa It Ac Jp Infolib Cont 01 Grepository 000 000 Pdf

Mosfetスケーリング マイクロ ナノデバイス

半導体業界の話題 第9回 エレクトロニクス業界の発展を牽引してきた ムーアの法則 はさらに続く ピックアップ プリント基板の窓口 プリント基板設計 製造 実装の最適な発注先が見つかる

チャネル長変調 Wikipedia

Www Ieice Hbkb Org Files S2 S2gun 01hen 03 Pdf

Ascii Jp 半導体プロセスまるわかり カーボンナノチューブと450mmウェハー 2 3

0 15µm Fd Soi低電力lsi技術 849kb

Www Ieee Jp Org Section Tokyo Chapter Ed 15 07 Hiroshima Miura 2 Pdf

Finfetのアナログ適用 デジタル回路が不可欠 日経クロステック Xtech

東北大 高性能 サブ10nm 3次元フィン型ゲルマニウムトランジスタ作製に成功 Fabcross For エンジニア

短チャネル効果について質問です マルチゲートにすることで ゲー Yahoo 知恵袋

Ascii Jp 半導体プロセスまるわかり カーボンナノチューブと450mmウェハー 2 3

コメント

コメントを投稿